Microprocessor Architecture

2.1 Components of a Microprocessor

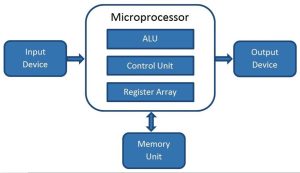

A microprocessor is composed of several key components that work together to process data and execute instructions. The three main components are:

1. Arithmetic Logic Unit (ALU):

The ALU is the mathematical brain of the microprocessors. It performs arithmetic operations (addition, subtraction, multiplication, division) and logical operations (AND, OR, NOT, XOR). The first commercial ALU was the Intel 74181, released in 1970 as part of the 7400 series TTL integrated circuits.

2. Control Unit:

The control unit coordinates the activities of other components by interpreting instructions and generating control signals. It manages the fetch-decode-execute cycle and directs the flow of data between the ALU, registers, and memory.

Figure 1: Microprocessor Architecture

3. Registers:

Registers are small, high-speed storage locations within the processor. They store temporary data, instructions, and memory addresses. Common registers include:

- Program Counter (PC): Holds the address of the next instruction to be executed.

- Instruction Register (IR): Stores the current instruction being decoded and executed.

- Memory Address Register (MAR): Holds the memory address for read/write operations.

- Memory Data Register (MDR): Temporarily stores data being transferred to/from memory.

- General Purpose Registers: Used for various data storage needs during processing.

2.2 Bus Systems

Buses are communication systems that transfer data between components. There are three main types of buses in a microprocessor system.

1. Address Bus:

- Unidirectional (microprocessor to memory/I/O devices)

- Carries memory or I/O device addresses

- Width determines addressable memory (e.g., 16-bit bus can address 65,536 locations)

2. Data Bus:

- Bidirectional

- Transfers data between microprocessor and memory/I/O devices

- Width affects the amount of data transferred per cycle (e.g., 8-bit bus can transfer values 0-255)

3. Control Bus:

- Bidirectional

- Carries control signals (read, write, interrupt, etc.)

- Coordinates operations between microprocessor and other components

2.3 Memory Organization

Memory in a computer system is organized in a hierarchy to balance speed, cost, and capacity:

- Registers: Fastest, smallest capacity, within the CPU

- Cache Memory: Very fast, small capacity, close to CPU

- Main Memory (RAM): Fast, larger capacity, directly accessible by CPU

- Secondary Memory: Slow, largest capacity, not directly accessible by CPU

This hierarchy is designed to optimize access times and storage capacity. Frequently used data is kept in faster, more expensive memory closer to the CPU, while less frequently used data is stored in slower, cheaper memory farther from the CPU.

2.4 Instruction Cycle and Fetch-Execute Process

The instruction cycle, also known as the fetch-decode-execute cycle, is the basic operational process of a CPU. It consists of several steps:

- Fetch:

- CPU retrieves instruction from memory address in Program Counter (PC)

- Instruction is loaded into the Instruction Register (IR)

- PC is incremented to point to the next instruction

- Decode:

- CPU interprets the instruction in the IR

- Determines the operation to be performed and identifies operands

- Execute:

- CPU performs the operation specified by the instruction

- May involve ALU operations, data transfers, or control flow changes

- Additional Steps (depending on architecture):

- Fetch operands: Retrieve data needed for instruction execution

- Store results: Write results back to memory or registers

- Interrupt handling: Check for and process any interrupts

This cycle repeats continuously as the CPU processes instructions. The efficiency of this cycle significantly impacts the overall performance of the microprocessor.

For further explanation: A video lecture following this reading material provides additional insights and clarifications

References:

[1] https://www.geeksforgeeks.org/introduction-of-alu-and-data-path/

[2] https://www.geeksforgeeks.org/bus-organization-of-8085-microprocessor/

[3] https://www.geeksforgeeks.org/memory-hierarchy-design-and-its-characteristics/

[4] https://www.geeksforgeeks.org/different-instruction-cycles/